# Quantum modulation of the channel charge and distributed capacitance of double gated nanosize FETs

# Ferdinand V. Gasparyan<sup>\*</sup> and Vladimir M. Aroutiounian

Department of Semiconductor Physics and Microelectronics, Yerevan State University, 1 Alex Manoogian St., Yerevan 0025, Armenia

(Received February 10, 2015, Revised March 29, 2015, Accepted March 30, 2015)

**Abstract.** The structure represents symmetrical metal electrode (gate 1) – front SiO<sub>2</sub> layer – n-Si nanowire FET – buried SiO<sub>2</sub> layer – metal electrode (gate 2). At the symmetrical gate voltages high conductive regions near the gate 1 – front SiO<sub>2</sub> and gate 2 – buried SiO<sub>2</sub> interfaces correspondingly, and low conductive region in the central region of the NW are formed. Possibilities of applications of nanosize FETs at the deep inversion and depletion as a distributed capacitance are demonstrated. Capacity density is an order to  $\sim \mu F/cm^2$ . The charge density, it distribution and capacity value in the nanowire can be controlled by a small changes in the gate voltages. at the non-symmetrical gate voltages high conductive regions will move to corresponding interfaces and low conductive region will modulate non-symmetrically. In this case source-drain current of the FET will redistributed and change current way. This gives opportunity to investigate surface and bulk transport processes in the nanosize inversion channel.

Keywords: quantization; charge modulation; nanosize FET; capacity

## 1. Introduction

Capacitors are important components in many integrated circuits. They serve numerous roles in analog and mixed signal circuits, including switched capacitor filters. Capacitors provide a vital role in the decoupling of microprocessors, digital signal processors, and microcontrollers from power supply variations.

The nanotube and nanowire devices can be used as capacitors. In semiconductor nanowires (NW), due to the size quantization, the conductance exhibits quantum effects. It is necessary to take these effects into account in future electronic circuits of nanometer dimensions. It would be also possible to construct new devices with some unique functionality. Note that the ability to control physical properties of semiconducting nanowires has made them attractive devices to study quantum effects at a very small scale. Nanotubes and nanowires dramatically boost the amount of surface, and thus electrical charge, that each metal electrode can possess. The potential for smaller and more powerful capacitors might prove crucial in developing microchips with ever denser circuitry. Moreover, such nanoscale capacitors might help improve the development of compact and cost effective supercapacitors. The nanoscale capacitors might also serve in advanced memory

<sup>\*</sup>Corresponding author, Professor, E-mail: fgaspar@ysu.am

chips.

Multi-component nanowire structures in coaxial configuration, such as p-type/intrinsic/n-type silicon nanowire (Tian et al. 2007) and metal-insulator-metal (MIM) nanowires (Banerjee et al. 2008, Kemell et al. 2007, Klootwijk et al. 2008, Shelimov et al. 2000) have promising applications as fundamental building blocks in future electronic (Tian et al. 2007, Kempa et al. 2008), photonic (Liu et al. 2011), power storage and delivery devices (Banerjee et al. 2008, Kemell et al. 2007, Klootwijk et al. 2008, Shelimov et al. 2000). High-density and flexible capacitors are in high demand with the rapid growth of renewable energy industry. Values of MIM micro/nano-capacitors with capacitance densities ranging from 2.5 to 100  $\mu$ F/cm<sup>2</sup>, via depositing alternating metallic and insulating layers inside the anodic aluminum oxide nanopores are reported in (Banerjee et al. 2008, Kemell et al. 2007, Klootwijk et al. 2008, Shelimov et al. 2000). Such devices have high power density but low flexibility when integrating with two-dimensional architectures. Whereas a direct growth of similar structures may be much easier to integrate into flexible substrate, micro/nano-electromechanical system (Sazonova et al. 2004, Steele et al. 2009), lab-on-a-chip device (Daw and Finkelstein 2006) and so on. A single Cu-Cu<sub>2</sub>O-C (metal-insulatorcarbon) coaxial nanowire capacitor demonstrates also. Cu (inner core) and C (shell) serve as conducting layers and Cu<sub>2</sub>O - as an interfacial dielectric layer. The measured capacitance is 10–40 times larger than the value calculated based on a classic cylindered capacitor model. Remarkable capacitance density as high as 143  $\mu$ F/cm<sup>2</sup> is found for such nanowire capacitors, exceeding previously reported values of MIM micro/nano-capacitors (Banerjee et al. 2008, Kemell et al. 2007, Klootwijk et al. 2008, Shelimov et al. 2000). The Cu-Cu<sub>2</sub>O-C nanowires also exhibit high electrical conductivity, current-carrying capacity, as well as excellent thermal stability. Quantum mechanical calculations indicate that this unusually high capacitance may be attributed to a negative quantum capacitance of the dielectric-metal interface, enhanced significantly at the nanoscale (Liu et al. 2012).

In 1993, electrical conductance quantization was found in gold nanowires made with the scanning tunneling microscope technique at room temperatures (Pascual *et al.* 1993). The electrical models that have been developed for carbon nanotubes for use in the development of a carbon nanotube capacitor model are reviews in Refs. (Budnik *et al.* 2009a, b).

Note that the local charge concentration and hence the conductance of the nanowires was quite sensitive to small changes of the gate voltage.

## 2. Nanowire capacitance behavior

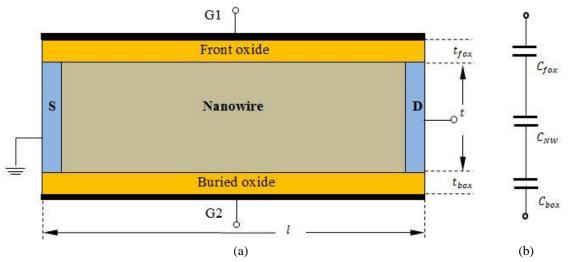

Nanosized FETs are the main active parts for lot of nanosized bio- and chemical sensors and other sensitive devices. The schematic picture of the investigated structure is presented on Fig. 1. The structure represents symmetrical metal electrode (gate 1, G1) -front oxide (fox) layer - NW - buried oxide (box) layer - metal electrode (gate 2, G2). Nanowire has n-type conductivity Si, fox and box are SiO<sub>2</sub> layers having the same sizes. It can be regulated source-drain current in the lateral NW FET by the changing gate voltages. We take the simple case of equality of gate voltages  $|V_{g1}| = |V_{g2}|$  for physical explaining and numerical estimation in further. Source of the lateral FET connected on ground. After applying gate voltages within in the NW near the fox and box layers the deep accumulation (inversion) and depletion layers can be formed, correspondingly. As it is known, size quantization effect appears in the inversion layer of NW FETs (Pud *et al.* 2014) that brings to specific redistribution of the charge carriers inside NW. In the quantum case, a

Fig. 1 Schematic picture (a) and equivalent capacitive scheme (b) of the investigated structure. S and D are source and drain, t,  $t_{fox}$  and  $t_{box}$  are thicknesses of the NW, fox and box layers, correspondingly, l is the length of NW

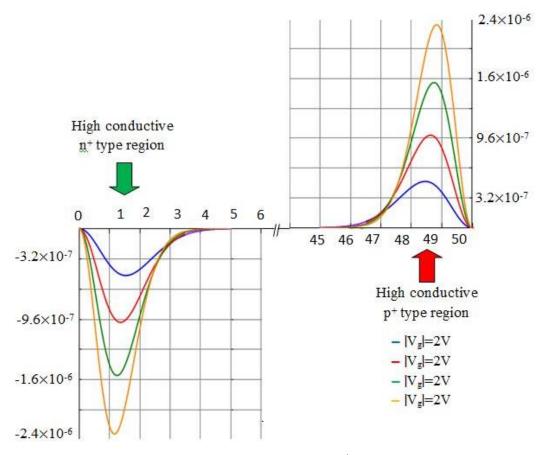

conception of the uniform inversion layer approximation becomes inappropriate. Recently we show that in the case switch off back gate (G2) voltage, the growth of the G1 gate voltage  $(V_{g1} > 0)$  results in an increase in the maximal concentration of electrons and also in a shift of its maximum towards the fox-nSi NW interface (see Fig. 5(b) in (Pud *et al.* 2014)). The majority of the electrons is located near fox layer and occupies the region at a depth of 1-2 nm. The maximum of electron concentration moves away from the interface into the depths of the NW depending on applied gate voltage. In the case of the switch on both front and back gate voltages ( $|V_{g1}| = |V_{g2}|$ ;  $V_{g2} < 0$ ) in the NW near the box deep depletion region is formed. This positive charge region is conditioned by the ionized donor atoms in the NW. In this case maximal value of the expressions (15), (4), (7) of Ref. (Pud *et al.* 2014) and using same electro-physical and geometrical parameters of oxide layers and NW (we take equality of the fox and box layer's thicknesses  $t_{fox} = t_{box} = 10$  nm) present on Fig. 2.

It is clear that regulation of the low conductive region width will be more effective for the small thickness NW. In this case by the small changing of the gate voltages ( $V_{g1}$  and  $V_{g2}$ ) we can effectively cover low conductive region. Voltage-dependent capacitance density  $C_{NW}$  can be defined as follows

$$C_{NW}(V_g) = \frac{dQ(x,V_g)}{dV_g}.$$

(1)

Here Q is the charge density of the high conductive region that is equal to

$$Q(x, V_g) = \frac{eN}{A} = \frac{e\Omega n(x, V_g)}{A} = \frac{elwt'n(x, V_g)}{lw} = et'n(x, V_g),$$

(2)

where e is the elementary charge, N is the total number of electrons,  $n(x, V_q)$  is the electron

Fig. 2 Distribution of the charge density in the n-SiNW having  $t' \approx 2$  nm average effective thickness in the case  $|V_{g1}| = |V_{g2}| \equiv |V_g|$

concentration depending on coordinate x and gate voltage, A = wl is the capacitor plate area,  $\Omega$  is the volume and t' is the effective thickness of the high conductive region, correspondingly, x is the coordinate on the direction from fox/box-NW interface.

Substituting Eq. (2) into Eq. (1) we have

$$C_{NW}(V_g) = et' \times \frac{dn(x, V_g)}{dV_g}.$$

(3)

The position of the maximal concentration of electrons  $x_m$  depends on gate voltage as follows (see Fig. 10 in Pud *et al.* (2014))

$$x_m \approx 1.21 + 1.64 \times exp(-0.88V_g)$$

nm. (4)

Using the value at the electron maximum concentration  $x = x_m$ , we can define the maximal value of capacitance density  $C_{NW}(V_g)_m$

$$C_{NW}(V_g)_m \approx et' \times \frac{n(x_m, V_g)}{V_g} = \frac{Q_m}{V_g}.$$

(3a)

Here  $Q_m$  is the maximal charge density of the high conductive region. On the Fig. 2 electrical charge distribution in the accumulation/inversion and depletion layers near the fox-NW and box-NW interfaces are presented for the several values of the applied gate voltages. Those dependencies plotted using corresponding expressions and same data which we use in (Pud *et al.* 2014). Near the fox and box layers high conductive regions are formed. Between the two high conductive regions (as a capacitor plates) and low conductive central region (as an insulator) capacitance  $C_{NW}$  is formed (see Fig. 2, Fig. 1(b)). It is distributed capacitance.

Total measurable capacitance C between electrodes G1 and G2 is equal to

$$\frac{1}{c} = \frac{1}{c_{fox}} + \frac{1}{c_{NW}} + \frac{1}{c_{box}} \quad .$$

(5)

Here  $C_{fox}$  and  $C_{box}$  are capacitances of the fox and box layers, correspondingly

$$C_{fox/box} = \frac{\varepsilon \varepsilon_0}{t_{fox/box}}.$$

(6)

Here  $\varepsilon$  and  $\varepsilon_0 = 8.85 \times 10^{-14}$  F/cm are the dielectric permittivity of silicon dioxide and free space, correspondingly.

We can estimate maximal values of the capacitance densities from data of Fig. 2 and Eqs. (3a), (5) and (6). They are:  $C_{NW} = 0.24 \ \mu\text{F/cm}^2 (|V_{g1}| = |V_{g2}| = 2 \text{ V})$  and 0.45  $\mu\text{F/cm}^2 (|V_{g1}| = |V_{g2}| = 5 \text{ V})$ ,  $C_{fox} = C_{box} = 3.4515 \ \mu\text{F/cm}^2$ . Finally for our case:  $C \approx 0.2 \ \mu\text{F/cm}^2$  at the  $|V_{g1}| = |V_{g2}| = 2 \text{ V}$  and  $C \approx 0.4 \ \mu\text{F/cm}^2$  at the  $|V_{g1}| = |V_{g2}| = 5 \text{ V}$ .

#### 3. Conclusions

We demonstrate the possibility of the application of the nanosize FETs at the deep accumulation/inversion and depletion as a regulated distributed capacitance. Without any special constructions and new additions it can be achieved capacity value an order to  $\sim \mu F$ . Those values are smaller as compared with reference data for nanosized MIMs and metal-insulator-carbon capacitors. They can be have special promising applications in the field of nanosized electronics, bio-electronics, medicine, as fundamental building blocks in future electronic, photonic, power storage and delivery devices.

Note that at the non-symmetrical gate voltages when  $|V_{G1}| \neq |V_{G2}|$  high conductive regions will move to corresponding interfaces and low conductive region will modulate nonsymmetrically. In this case source-drain current will redistributed and change current way. This gives opportunity to investigate surface and bulk transport processes in the nanosize inversion channel. In near future electronic circuits of nanometer dimensions it would be necessary to take this effect into account and it would be also possible to construct new devices with some unique functionality. Investigation of the peculiarities of the nanosized capacitors made them attractive devices to study quantum effects at a very small scale.

### References

Banerjee, P., Perez, I., Henn-Lecordier, L., Lee, S.B. and Rubloff, G.W. (2009), "Nanotubular metalinsulator-metal capacitor arrays for energy storage", *Nat. Nano.*, **4**(5), 292-296.

- Budnik, M.M. (2009), "Carbon nanotube capacitors", *Cutting Edge Nanotechnology*, Ed. A. Lazinica, Intech, Vienna, Austria.

- Budnik, M.M. and Johnson, E.W. (2009), "A carbon nanotube capacitor", *Proceedings of the 2009 IEEE Nanotechnology Materials and Devices Conference (NMDC)*, Traverse City, MI, USA, June.

- Daw, R. and Finkelstein, J. (2006), "Lab on a chip", Nature, 44 (7101), 367-367.

- Kemell, M., Ritala, M., Leskela, M., Ossei-Wusu, E., Carstensen, J. and Föll, H. (2007), "Si/Al<sub>2</sub>O<sub>3</sub>/ZnO:Al capacitor arrays formed in electrochemically etched porous Si by atomic layer deposition", *Microelectron. Eng.*, 84(2), 313-318.

- Kempa, T.J., Tian, B., Kim, D.R., Hu, J., Zheng, X. and Lieber, C.M. (2008), "Single and tandem axial p-i-n nanowire photovoltaic devices", *Nano Lett.*, 8(10), 3456-3460.

- Klootwijk, J.H., Jinesh, K.B., Dekkers, W., Verhoeven, J.F.C., Van den Heuvel, F.C., Kim, H.D., Blin, D., Verheijen, M.A., Weemaes, R.G.R., Kaiser, M., Ruigrok, J.J.M. and Roozeboom, F. (2008), "Ultrahigh capacitance density for multiple ALD-grown capacitor stacks in 3-D silicon", *Elect. Dev. Lett.*, IEEE, 29(7), 740-742.

- Liu, W.F., Oh, J.I. and Shen, W.Z. (2011), "Light adsorption mechanism in single c-Si (core)/a-Si (shell) coaxial nanowires", *Nanotechnology*, 22(12), 125705.

- Liu, Z., Zhan, Y., Shi, G., Moldovan, S., Gharbi, M., Song, L., Ma, L., Gao, W., Huang, J., Vajtai, R., Banhart, F., Sharma, P., Lou, J. and Ajayan, P.M. (2012), "Anomalous high capacitance in a coaxial single nanowire capacitor", *Nat. Commun.*, 3(1), 879-885.

- Pascual, J.I., Mendez, J., Gomez-Herrero, J., Baro, A.M., Garcia, N. and Thien Binh, V. (1993), "Quantum contact in gold nanostructures by scanning tunneling microscopy", *Phys. Rev. Lett.*, **71**(12), 1852-1855.

- Pud, S., Gasparyan, F., Petrychuk, M., Li, J., Offenhäusser, A. and Vitusevich, S.A. (2014), "Single trap dynamics in electrolyte-gated Si-nanowire field-effect transistors", J. Appl. Phys., 115(23), 233705-11.

- Sazonova, V., Yaish, Yu., Ü stünel, H., Roundy, D., Arias, T.A. and McEuen, P.L. (2004), "A tunable carbon nanotube electromechanical oscillator", *Nature*, 431(7006), 284-287.

- Shelimov, K.B., Davydov, D.N. and Moskovits, M. (2000), "Template grown high-density nanocapacitor arrays", *Appl. Phys. Lett.*, **77**(11), 1722-1724.

- Steele, G.A., Hüttel, A.K., Witkamp, B., Poot, M., Meerwaldt, H.B., Kouwenhoven, L.P. and Van der Zant, H.S.J. (2009), "Strong coupling between single-electron tunneling and nanomechanical motion", *Science*, 325(5944), 1103-1107.

- Tian, B., Zheng, X., Kempa, T.J., Fang, Y., Yu, N., Yu, G., Huang, J. and Lieber, Ch.M. (2007), "Coaxial silicon nanowires as solar cells and nanoelectronic power sources", *Nature*, 449(71), 885-889.

CC